Relazione per l’esame di

ELETTRONICA DEI SISTEMI DIGITALI

Ing. Elettronica - Politecnico di Bari

A.A. 1997/98

" Progetto e realizzazione di un frequenzimetro digitale "

CARLO DIOMEDE ***** GIUSEPPE BATTISTA

SOMMARIO

INTRODUZIONE

Il frequenzimetro o contatore di frequenza , è uno strumento digitale che viene utilizzato per misurare la frequenza di un segnale in genere sinusoidale . Esso è costituito essenzialmente da un contatore in grado di contare il numero di impulsini sincroni al segnale in una determinata frazione temporale stabilita in fase di progetto. Dividendo il numero di impulsi contati per il periodo di osservazione si ottiene la frequenza incognita o meglio una sua stima , la cui precisione dipende da numerosi fattori riguardanti la scelta dei dispositivi reali del circuito e l’effettivo grado di sincronismo ottenibile nel circuito tra il segnale misurando e un segnale generato all’interno del frequenzimetro come riferimento detto segnale base dei tempi. Facendo in modo che il tempo di conteggio degli impulsi sia unitario si ottiene dal contatore un numero di conteggi numericamente uguale alla frequenza incognita. Tale realizzazione è da considerarsi di natura prettamente sperimentale e didattica e le prestazioni del circuito , a riguardo soprattutto della massima frequenza misurabile sono assai limitate rispetto ai risultati ottenibili oggi con dispositivi "all in one" che incorporano in maniera integrata tutte le funzioni dei blocchi che costituiscono il frequenzimetro. La maggior compattezza dei circuiti ottenibili con tali apparati garantisce ottime prestazioni in frequenza . Un esempio di tali circuiti integrati è l’ ICM-7216D con il quale si possono realizzare frequenzimetri capaci di misurare una frequenza fino ai 30 MHz e con l’impiego di opportuni circuiti prescaler ci si può spingere facilmente ai 600 MHz. Non si è optato per un progetto del genere a causa del fatto che non si avrebbe focalizzato l’attenzione verso quelle problematiche di progetto inerenti al corso e cioè al dimensionamento temporale del sistema , all’utilizzo di celle di memoria fondamentali , al dimensionamento di contatori e all’utilizzo di decodificatori BCD a led. In base a tali esigenze didattiche , probabilmente sono state fatte da noi scelte tecnicamente inefficenti , ma , mi ripeto , tale esperienza si prefigge di giungere ad un progetto funzionante a partire dalle nozioni di base del corso e quindi utilizzando dispositivi , che se pur in forma integrata , sono comunissimi contatori e decodoficatori , nonché transistors e diodi discreti e quindi componenti semplici che al massimo contengono poche porte logiche.

DESCRIZIONE DELL’ESPERIENZA

Tale esperienza è stata realizzata seguendo i seguenti passi :

Per quanto riguarda le simulazioni al calcolatore , sono stati utilizzati i softwares Pspice 6.0 della Microsim ed Electronics Workbench 4.0 della Interactive , entrambi in versione di valutazione.

FUNZIONAMENTO DEL FREQUENZIMETRO

Possiamo dare uno sguardo allo schema a blocchi di questo frequenzimetro , che pur nella sua semplicità costituisce il fondamento di progetto di qualsiasi strumento del genere . Per la descrizione dello schema a blocchi seguiamo il percorso del segnale misurando s(t) : esso viene generato da un oscillatore a frequenza fissa ed incognita da un circuito esterno che utilizza l’integrato LM555.Tale segnale non ha bisogno di ulteriori processi in quanto è già di forma rettangolare e ad un livello di tensione compatibile con la logica TTL dello strumento . Contemporaneamente viene generata la base dei tempi b(t) grazie ad un preciso oscillatore al quarzo da 10 MHz contrassegnato con Xtal seguito da una serie di divisori di frequenza realizzati con contatori decadici asincroni. b(t) passa attraverso un JKFF in configurazione toggling (TFF) che funge da divisore di frequenza dandoci il segnale d(t) che ci permette di ottenere la finestra temporale unitaria per il campionamento . Tale segnale viene introdotto insieme ad s(t) in una porta and la cui uscita è collegata al contatore a 4 digits decimali costruito con 4 integrati del tipo 74AS90 dotati di un un morsetto di reset del conteggio. Tale morsetto è collegato direttamente ad un altro LM555 che funge da monostabile . Quest’ultimo viene eccitato dal fronte di salita del segnale a(t) ottenuto da un altro TFF collegato all’uscita del precedente TFF . Il contatore pilota 4 decoder driver a 4 bit che a loro volta pilotano i display a led a 7 segmenti. I registri in configurazione PIPO servono a mantenere memorizzati per un certo tempo i valori di conteggio per evitare un fastidioso sfarfallio dei display. La durata della finestra temporale può essere scelta in base al deviatore D che commuta o il segnale b1(t) ad 1 kHz oppure il segnale b2(t) ad 1 Hz , garantendo rispettivamente il conteggio quindi la misura della frequenza di s(t) , in kHz o in Hz.

ANALISI DEL CIRCUITO

Analizziamo ora dal punto di vista quantitativo le parti principali del circuito del frequenzimetro , considerandole per ora a se stanti , ribadendone le specifiche di progetto . Per ogni circuito viene dato lo schema circuitale con riferimento ai dispositivi utilizzati , la netlist relativa alla simulazione ed una simulazione grafica:

Oscillatore campione per la base dei tempi

E’ costituito da un oscillatore a quarzo ottenuto da un anello in porte not reazionato . E’ utilizzato un IC 74SN04 . I due resistori da 680 ohm costituiscono un partitore simmetrico ; il quarzo ha una frequenza di risonanza di 10.240 MHz ed è stato ottenuto da un canalizzatore PLL surplus di un ricetrasmettitore CB.

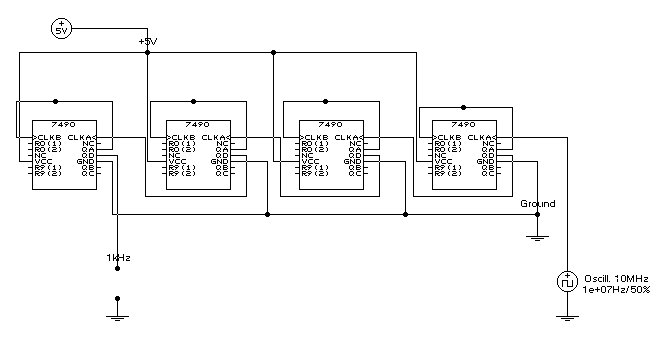

Divisore di frequenza per la base dei tempi

Abbiamo utilizzato 7 contatori decadici del tipo 74AS90 che sono costiuiti internamente da contatori asincroni (ripple counter) con TFF . Nello schema ne appaiono soltanto 4 perché gli altri 3 servono per abbassare la base dei tempi ad una frequenza di 1 Hz che serve per l’altra scala di misura (periodo di gate 1 sec.). Essendo , in realtà , il segnale di uscita con un duty cycle (DC) del 20% abbiamo previsto successivamente un altro TFF per ottenere la vera e propria base dei tempi. Nella simulazione grafica è possibile confrontare i duty cycle ottenuti.

La simulazione non mostra la periodicità del segnale ad 1 kHz perché la base dei tempi (0.5us.) è troppo breve. Una simulazione a parte per questo segnale ha dato il risultato voluto. Sono da notare i DC di tutti i segnali in uscita dai divisori di frequenza ; hanno tutti un valore del 20% come avevamo affermato in precedenza.

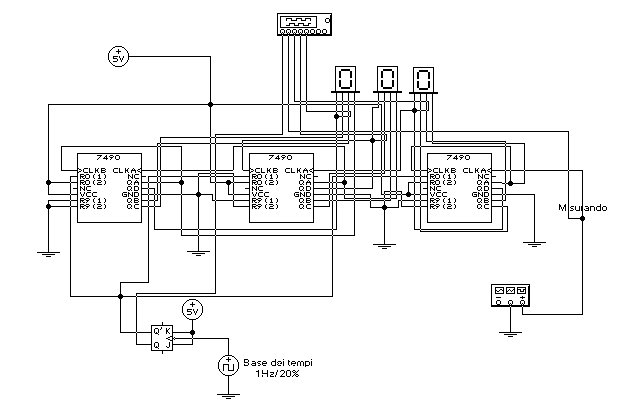

Contatore a 4 digits (mod 10000)

Lo

schema in figura è costituito solo da 3 digits per questioni di

efficienza ma il quarto digits , con il relativo 7490 si collega

esattamente come gli altri.Il generatore di funzione da 1Hz

DC=20% simula l’uscita dal divisore di frequenza visto prima

, mentre il segnale misurando è un segnale rettangolare. Anche

qui utilizziamo una simulazione con l’Electronics Workbench

perché la versione di Pspice a nostra disposizione può simulare

fino ad un limite massimo di nodi che con questi circuiti

composti da più flip-flops viene superato.

Lo

schema in figura è costituito solo da 3 digits per questioni di

efficienza ma il quarto digits , con il relativo 7490 si collega

esattamente come gli altri.Il generatore di funzione da 1Hz

DC=20% simula l’uscita dal divisore di frequenza visto prima

, mentre il segnale misurando è un segnale rettangolare. Anche

qui utilizziamo una simulazione con l’Electronics Workbench

perché la versione di Pspice a nostra disposizione può simulare

fino ad un limite massimo di nodi che con questi circuiti

composti da più flip-flops viene superato.

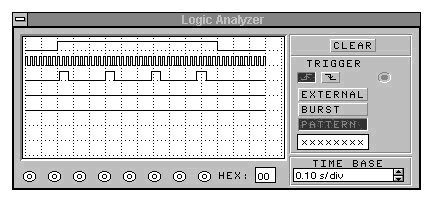

Si può notare il periodo di gate di un secondo , il segnale misurando (in questo caso la frequenza incognita è di 35 Hz) , e gli impulsi di conteggio dei multipli di 10 (sono 4 perché il primo impulso si ha in corrispondenza dell’azzeramento). Gli altri segnali sono bassi perché il numero di impulsi da conteggiare è troppo piccolo per azionare i rispettivi contatori.

Circuito completo del frequenzimetro

A differenza degli schemi esmplificativi visti prima , in questo schema vediamo esattamente la soluzione adottata per il problema del sincronismo del reset di conteggio . I due TFF contenuti nell’integrato 74107 fungono l’uno da divisore di frequenza (è utile anche per simmetrizzare il DC) e l’altro sempre da divisore di frequenza ma pilota il monostabile per ottenere mezzo periodo prima del tempo di gate il reset del contatore. Tutto diviene più chiaro guardando il diagramma temporale della figura.

Nella figura successiva , possiamo vedere , invece l’intero circuito del frequenzimetro. Abbiamo utilizzato sempre lo schematics dell’Electronics Workbench.

SCELTA DEI COMPONENTI REALI

Le specifiche che i componenti devono rispettare sono essenzialmente quelle riguardanti i tempi di commutazione. Infatti tutti i problemi relativi alle dinamiche di ingresso dei dispositivi vengono automaticamente risolti impiegando dispositivi della stessa famiglia logica (in questo caso TTL) e verificando che le caratteristiche massime di carico (fan in e fan out) non vengano superate. Il problema dei tempi di commutazione e dei tempi di propagazione del segnale sono legati , nel caso del frequenzimetro con la massima frequenza misurabile . Il legame non è però diretto , cioè è vero che , per esempio se utilizzassimo l’integrato 74SN90 per il contatore (tp=10 ns. f=30MHz) non sarebbe vero che il nostro frequenzimetro potrebbe misurare la frequenza di un segnale a 30MHz. Infatti il limite è stabilito , anche dal progetto del circuito. Infatti il contatore mod 10000 è costituito da 4 contatori decadici asincroni (ripple counters) , e visto che il tempo di propagazione totale del contatore è dato dalla somma di tutti i tempi , allora si ha T=4x(4x10ns.)=160ns. con un’equivalente frequenza massima fmax=1/T=6.25MHz . Tale limitazione aggiuntiva non è quindi giustificata da difficoltà intrinseche dei dispositivi ma dal fatto che , essendoci ritardi finiti , potrebbero esserci problemi di sincronismo tra i diversi flip-flops di ogni integrato , e tra ogni integrato stesso. Quindi se volessimo , come nel nostro caso , misurare con la scala dei kHz una frequenza di 4 digits , dovremmo misurare almeno 10MHz. E’ impensabile accontentarsi dei 74SN90 dove SN sta per serie standard . Avremmo voluto puntare sul 74AS90 che presenta una tp=1.7ns. a cui corrisponde una fmax=36.8MHz ben dimensionata per i nostri scopi. Per questioni di reperibilità ci siamo limitati al 74LS90 con una tp=9ns. Per il divisore di frequenza , invece non ci sono problemi di sincronismo ma ci interessa soltanto il tp del flip-flop che lavora a frequenza maggiore. La frequenza maggiore è quella dell’oscillatore cioè 10MHz ben al di sotto del limite di 30MHz del 74SN90. Quindi , per il divisore di frequenza ci andrebbero bene anche gli integrati standard , ma , visto che la prudenza non è mai troppa , e che le differenze di costi sono limitate , abbiamo optato anche qui per i 74LS90. Merita qualche commento anche l’oscillatore realizzato con le porte not ad anello. Va bene il 74LS04 perché la frequenza di oscillazione è di 10MHz che è ben al di sotto della fmax. Lo stesso discorso vale per il 74LS112 che ci serve per realizzare i due JKFF in configurazione toggling .Vediamo nelle figure successive i data sheets degli integrati di cui sopra :

SINTESI MEDIANTE ASM DEL NEGATIVE EDGE TRIGGERED JKFF

Con il metodo delle mappe a campi si hanno le seguenti equazioni degli stati futuri :

SA = BCk’J SB = CkA + Ck’K’A

RA = B’Ck’K RB = (Ck’A + (Ck’J’)’A’)’

Che corrispondono ad una macchina a stati finiti equivalente al JKFF reale utilizzato nella nostra esperienza , contenuto nell’integrato 74LS112.

ANALISI DEI COSTI

La realizzazione di tale progetto ha richiesto anche informazioni sui prezzi di mercato dei dispositivi utilizzati. In particolare abbiamo voluto effettuare il confronto tra i costi relativi al nostro progetto ed un tipico progetto di frequenzimetro utilizzante un integrato "all in one" come il ICM-7216 prelevato da un numero di Radio Rivista. Abbiamo ottenuto questi risultati:

- Progetto personale £. 85.000

- Progetto con 7216 £. 67.000

Quindi è evidente anche qui il risparmio derivato dall’utilizzo di integrati tuttofare in quanto si semplifica molto il resto del circuito , diminuisce il numero di componenti utilizzati e diminuisce la complessità delle connessioni nonché l’estensione dell’eventuale circuito stampato o millefori.

CIRCUITI DI SUPPORTO

Ovviamente , per funzionare , il nostro circuito esige di una dovuta alimentazione , che rispetti sia la necessaria stabilità che il dovuto bisogno energetico. Abbiamo utilizzato , quindi un circuito stabilizzatore molto comune , realizzato con un LM7805CV capace di una tolleranza massima del 5% a pieno carico , ed una corrente massima di 1.4 A , più che sufficiente per l’intero circuito.Inoltre abbiamo realizzato a parte un multivibratore astabile a frequenza variabile con un integrato LM555 , calibrato per una frequenza di circa 70 kHz .Possiamo ricavare i tempi di livello alto (Th) e basso (Tl) con le seguenti formule :

Th = 0.693 x ( Ra + Rb ) x C Tl = 0.693 x Rb x C

Nel nostro caso si ha Th=7us. e Tl=7us. cioè la frequenza è 1 / (Th + Tl) = 71.8 kHz.

BIBLIOGRAFIA

ATTREZZATURA UTILIZZATA

Vai al sito di Carletto Diomede